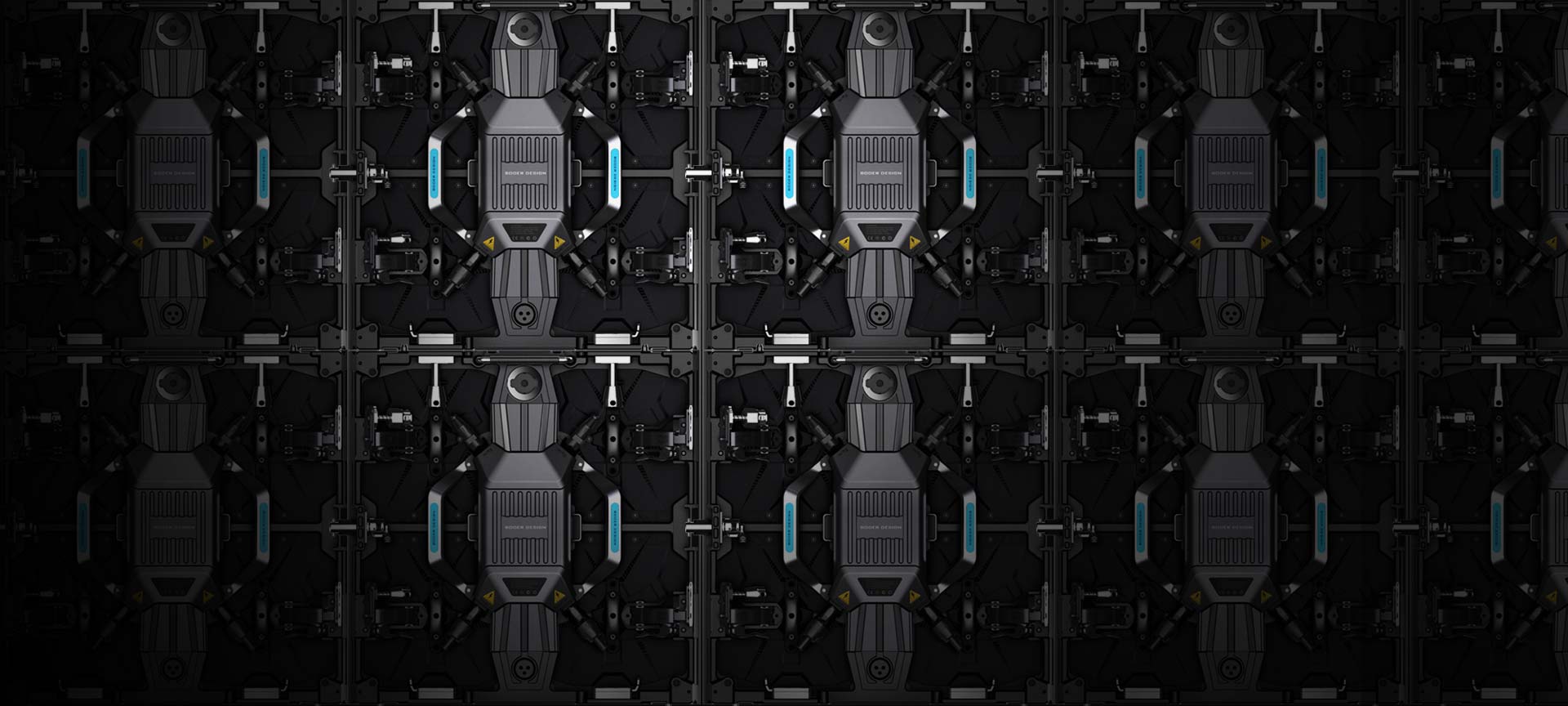

提及LED拼接器产品外观设计,拼接器的一个关键应用是可以输出多路DVI信号,对矩阵排列的多个显示屏进行拼接显示,使之成为逻辑上的一个完整的显示区域。

随着LED小间距产品的显示面积越来越大,几十平方米的项目屡见不鲜,LED显示屏的物理分辨率往往会超过1920×1200,即每一块超大规模的LED显示屏,都是由若干个LED控制器所驱动的若干个独立的显示区域组成的,对于拼接器的应用而言,只需要对应LED控制器的数量提供若干个DVI输出接口,并对整个LED屏幕进行拼接显示即可。

小间距LED图像拼接处理器的要求

(1)证输出同步性,避免拼接画面不同步现象;

(2)优化图像处理算法,使经过缩放处理的图像保持高清晰度;

(3)自定义输出分辨率,应对LED显示屏物理分辨率不规则的特点。LED拼接器产品外观设计

2、应用于小间距LED显示屏的拼接处理技术

小间距LED显示屏拼接器的关键技术:

(1)信号的输出同步性

拼接器的多路DVI信号输出,必然存在信号的同步性问题。不同步的信号输出到LED显示屏上,在拼接处就会出现画面撕裂现象,在播放高速运动的图像时尤为明显。如何保证信号的输出同步性,成为衡量一个拼接系统成败的关键。

(2)图形处理算法

我们知道,点对点的图像显示效果是最好的,经过缩小处理后的图像,如果仅采用普通的图形处理技术或通用的FPGA图形处理算法,图像的边缘会出现锯齿,甚至会出现像素缺失,图像的亮度也会下降。而高端的图像处理芯片或利用复杂图形处理算法的FPGA系统会最大限度的保证缩小后图像的显示效果。因此,好的图形处理算法是一款应用于小间距LED显示屏的拼接器的关键技术。LED拼接器产品外观设计

(3)非标准分辨率的输出

小间距LED显示屏是由一块一块相同规格的显示单元矩阵拼接而成,每个显示单元尺寸和物理分辨率是固定的,但是拼接起来的整个大屏幕,往往不是一个标准的物理分辨率。比如,显示单元的分辨率为128×96,只能拼成1920×1152,却拼不出1920×1080。在超大规模的拼接系统里,每台LED控制器所驱动的LED显示区域可能不是标准的分辨率,这个时候,拼接器具有非标准分辨率的输出就显得关键,它可以帮助我们快速找到合适的拼接方式,从而合理的分配资源,有效节约LED控制器和传输设备的使用数量。

应用于小间距LED显示屏的拼接器种类

目前拼接器可分为四类,即嵌入式纯硬件架构、PCI-E总线架构、分布式网络架构、混合架构。LED拼接器产品外观设计

(1)嵌入式纯硬件架构

整机结构通常会采用“背板+信号采集板+主控板+信号输出板”的设计,信号采集板进行诸如视频采集、缩放、叠加、格式转换等信号处理工作,通过背板总线将经过处理的信号传送给主控板的FPGA信号处理系统,通过嵌入式ARM系统实现对主控FPGA配置、与上位PC机通信、系统间的数据交换等功能,通过信号输出板将信号输出给显示终端。

纯硬件架构拼接器的结构相对简单、不容易出现系统故障;采集板和输出板可热插拔,易于更换;可实现多路、多格式信号的采集和处理;背板交换式技术和输出板卡统一时钟技术确保了多路信号输出的同步性;每一路DVI输出信号的分辨率均可自定义,符合LED显示屏的拼接特点。

诸多特点使纯硬件架构迅速成为当今拼接器领域的主流产品之一。但是,由于采用了FPGA作为核心的图像处理单元,算法的优劣决定了一款拼接器处理效果的好坏,尤其是图像缩放的算法,如何进行优化以达到更清晰的显示效果,已经成为判定纯硬件拼接器产品价值的重要指标。LED拼接器产品外观设计

(2)PCI-E总线架构

通常总线架构的拼接器采用PCI Express技术,可用数据带宽高达上百Gbps。主机配备高性能的CPU及大容量内存,可根据应用领域的不同预装不同的操作系统(如64位的Windows7),并可直接运行各种应用程序。拼接器配备多张高性能的图形输出卡,每张输出卡拥有超高的内部带宽及显存,并且所有的输出图像都被同步以消除显示单元间的图像撕裂。同时还配有多张输入卡,支持多种信号格式,并能够对输入信号进行图像处理。

PCI-E总线架构拼接器就是一台高性能的计算机,所有组件都选用各大硬件厂商最先进和成熟的技术,比如CPU可选用Intel,显卡可选用英伟达。所有计算机领域的高新技术也能够被快速的融合进来。这使得PCI-E总线架构拼接器在运算速度、图像处理、操作方式等方面具有无法比拟的优势。LED拼接器产品外观设计

PCI-E总线架构拼接器门槛很低,对于简单的应用,一台工控机,加上一个专业的多通道输出显卡即可实现。